别着急,坐和放宽

what is verilog

verilog HDL作为一种硬件描述语言,描述着数字电路的网络关系(电路结构)和逻辑,其编译产物为:

.vvp.vcd该产物是仿真结果生成波形图,编译器会先语法解析Parser,然后展开模块Elaboration,最后仿真生成波形Simulation Kernel.bit.sof该产物是FPGA配置文件用来烧录,流程是Verilog->Synthesis->RTL Netlist->Technology Mapping->Place & Route->Bitstream.gds该产物用于芯片设计.edf.v该产物是网表

我们编写的是RTL Verilog,一个例子:

module adder(

input [7:0] a,

input [7:0] b,

output [7:0] y

);

assign y = a + b;

endmodule

这个就是一个8Bit的加法器,其中:

module adder(input a,b, output y)是这个模块的名字adder以及其输入和输出数据assign是赋值关键字endmodule是模块结束关键字,和enddefine差不多

P1 语法学习

这里OJ主要以HDLBits为主

模块

类似cpp的函数,在verilog中,一个运行的子单元以模块为主,例如:

module example(

input a,b,

output y;

);

endmodule; // 结束模块关键字是必要的

这里的输入和输出端口也可以在模块外部写出

module example(a,b,c);

input a,b;

output c;

endmodule;

赋值

在verilog中赋值需要使用关键字assign后跟随方程进行赋值,例如一个简单的输出

module example(input a1,a2,a3, output y1, y2);

assign y1=a1, y2=a1, y2=a3; // 这里逗号用法和C/Cpp一样

endmodule;

导线

导线wire是实际设计中物理存在的符号,在verilog中作为一种存储的数据类型,与其对应的是reg,即寄存器类型

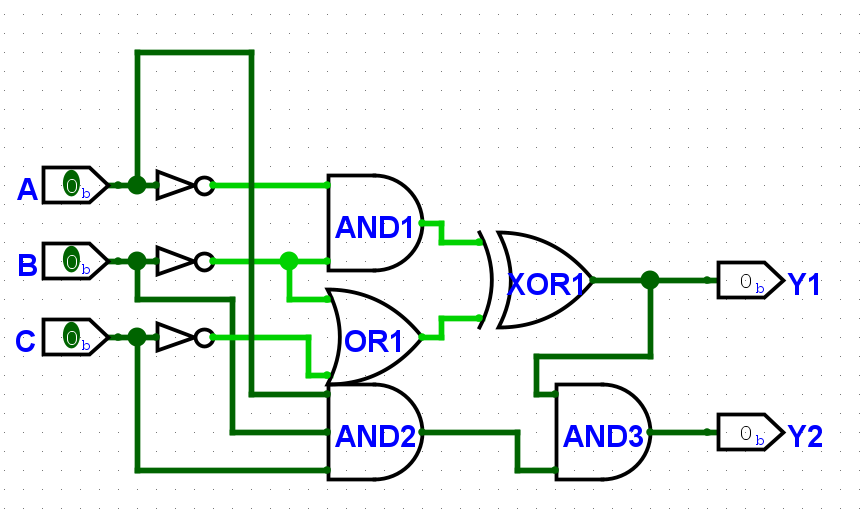

例如这一个模块(显然是可以化简):